2023-06-09 14:26:30

2023-06-09 14:26:30

1029

1029

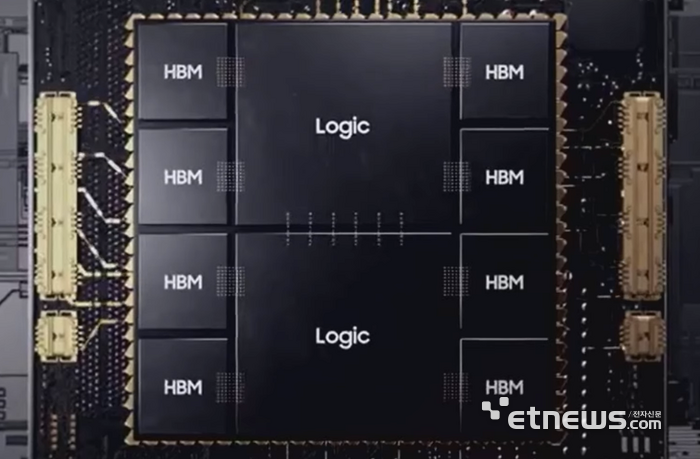

据韩媒报道,三星电子已经完成了“I Cube 8”的开发,这是一种可以集成多达8个高带宽存储器 (HBM) 的封装,并将于明年开始量产。

三星电子集团负责人金钟国在8日举行的半导体技术研讨会上表示,“未来半导体技术的竞争力将在于一个封装中可以集成多少逻辑和存储器。” 三星电子计划年内完成8个HBM的基础封装技术性能测试。

HBM是一种通过堆叠DRAM显著提高数据处理速度的存储器。由于内存堆叠水平高,它被认为是下一代封装技术,被归类为以人工智能(AI)、5G、云和数据中心应用为代表的高性能计算(HPC)的必需品。

随着以ChatGPT和超大规模数据中心为代表的生成AI需求的扩大,对大容量、运算速度快的内存需求也越来越大。2021 年,三星电子开发并量产了“I Cube 4”,它在一个封装中集成了四个HBM。继此次完成8个封装的开发后,三星计划通过推进搭载12个和16个HBM的封装技术的开发,引领先进封装市场。

随着HBM的扩展,封装和中介层面积也翻了一番。如果 iCube 4 的封装为 4225㎟,内插器为 1500㎟,则 iCube 8 的封装为 7225㎟,内插器为 2800㎟。配备12个HBM的iCube 12预计封装为7225㎟,内插器为3200㎟或更大。

做出这一决定是考虑到对“小芯片”不断增长的需求,小芯片将多个芯片连接成一个芯片,以克服单个芯片的性能限制和高成本。在2.5D封装工艺中,连接半导体印刷电路板(PCB)和芯片的中介层的作用很重要。

三星电子正在开发和升级垂直堆叠芯片的 3D 封装“XCube”。2020年首次亮相的第一代X-Cube技术已经应用于HBM,第二代技术已于去年完成可靠性验证,正在为量产做准备。

由于预计小芯片将决定下一代半导体市场的竞争力,三星电子计划通过封装以及优化结构、设计和工艺技术之间的协调来继续推进小芯片技术。

三星电子系统 LSI 部门负责人 Lee Kyung-min 表示:“通常小芯片被视为封装技术,但系统技术必须在结构、设计和处理领域做好准备,以实现可以作为单芯片。我们将确保和升级技术以克服超精细工艺技术和成本的限制,确保小芯片性能的优势,并提高功率效率。”